简介

AD4111集成了低噪声、快速建立、24位Σ-Δ型模数转换器(ADC)和模拟前端,支持全差分或单端、双极性±10 V电压输入和单端20 mA输入。AD4111设计用于工业自动化应用的可编程逻辑控制器(PLC)和分布式控制系统(DCS)模块。

本文详细介绍了AD4111电磁兼容性(EMC)印刷电路板(PCB)的功能,该电路板可与AD4111一起使用,支持典型的±10 V电压和0 mA至20 mA电流输入。电路板设计展示了一种针对工业自动化应用的验证EMC的解决方案。IEC 61000-4-x系列标准在系统层面讨论电气和电子设备抗扰度的评估。

AD4111 EMC测试板已经过一系列测试,以确保电路性能不受辐射射频(RF)或传导RF干扰的影响,并具有足够的抗静电放电(ESD)、电快速瞬变(EFT)和浪涌的能力。该板还针对CISPR 11进行了测试,其辐射发射水平远低于A类限值。

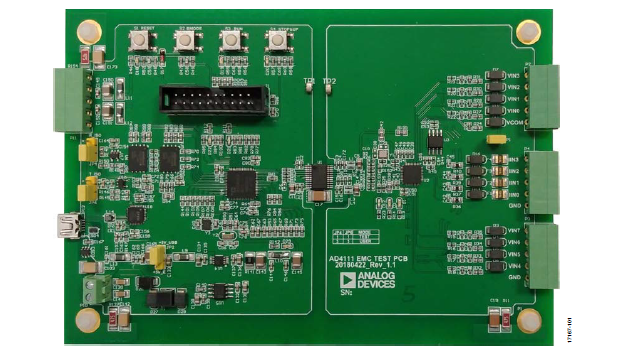

图4111 EMC测试板照片

系统设计

AD4111 ADC说明

AD4111是一款低功耗、低噪声、24位Σ-Δ型ADC,集成了模拟前端(AFE),支持全差分或单端双极性±10 V电压输入及0 mA至20 mA电流输入。对于完全建立的数据,AD4111的最大通道扫描速率为6.2 kSPS (161 μs)。

嵌入式2.5 V、低漂移(5 ppm/°C)带隙内部基准电压源(带输出基准电压缓冲器)减少了外部元件数量。数字滤波器提供灵活的设置,包括以27.27 SPS输出数据速率实现50 Hz和60 Hz同时抑制。用户可根据应用中每个通道的需求选择不同的滤波器设置。自动通道序列器支持ADC转接每个使能的通道。

AD4111的精密性能通过集成ADI公司专有的iPassives™技术而实现。该器件经过工厂校准,实现了非常高的额定精度。AD4111具有独特的电压输入开路检测功能(正在申请专利),可用于系统级诊断。该器件采用3 V或5 V单电源供电,很容易用于电气隔离应用。

有关详细信息,请参阅AD4111数据手册。

电路说明

AD4111专为涉及恶劣工业环境的PLC和DCS应用而设计。AD4111还符合IEC 6100-4-x和CISPR 11标准。

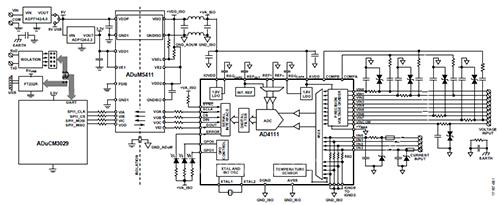

图2所示电路展示了一个采用AD4111的典型多通道、分组隔离、工业电压和电流输入模块,适用于恶劣的EMI和EMC状况。

在示例电路中,ADuCM3029超低功耗Arm® Cortex-M3微控制器单元(MCU)处理本地板载控制和与主机的数据通信。ADuM5411四通道隔离器集成DC-DC转换器,可实现整洁稳健的隔离模拟输入设计解决方案,采用3 V或5 V单电源供电。AD4111可以同时处理电流输入(单端或双极性差分电压输入)。

两个低压差稳压器(LDO)大大简化了示例电路中的板载电源,为电路板功能提供必要的电压。ADP7142将6 V至40 V输入电压降至5 V,为ADuM5411的初级端供电。ADP124将ADP7142输出调节至3.3 V,以用于微处理器和ADuM5411的数字隔离器部分。

这些电源的稳健性无意与典型工业自动化控制系统中的电源模块或背板电源相媲美,仅为供电电路实现了基本保护。该AD4111 EMC测试板可以选择使用主机的5 V通用串行总线(USB)电源正常运行,同时通过非隔离通用异步接收器发送器(UART)连接到USB端口与主机通信。当进行电磁兼容测试时,AD4111 EMC测试板改由一个独立的12 V直流电源供电,而数据通过板外隔离数据链路发送到主机。

图2. AD4111 EMC测试板电路框图

电路评估与测试

AD4111 EMC测试板可以连接到主机来运行,或在独立模式下运行。工作参数在板载闪存中编程。在辐射测试期间,测试板与主机断开连接,而固件运行,硬件保持工作状态。在抗扰度测试中,测试板通过隔离数据链路连接到主机。主机上的串行端口数据捕获程序从AD4111接收ADC转换样本。

EMC测试板上的AD4111仅进行过器件级的标准工厂校准,没有做进一步的电路板级校准。

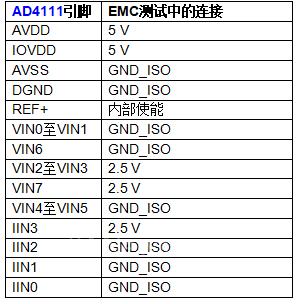

当输出数据速率设置为1007 SPS时,AD4111配置为连续对以下电压和电流输入通道顺序采样:VIN0至VIN1、VIN6、VIN2至VIN3、VIN7、VIN4至VIN5、IIN3、IIN2、IIN1和IIN0。当评估EMC测试的性能时,VIN2至VIN3代表差分电压输入通道,VIN7代表单端电压输入通道,IIN3代表电流输入通道。表1详细列出了EMC测试中的其他连接。

表测试中的AD4111引脚连接

在每次可能的破坏性EMC测试之前和之后,测试板采用独立的精密台式数字万用表(DMM)对2.5 V外部信号源进行采样。转换为电压或电流后,来自代表性通道的AD4111样本与同一期间DMM的测量结果进行比较,以量化误差。两个测量结果之间的偏差必须保持在预定范围内才能满足性能判据。最大允许误差为满量程的0.1%,这符合工业自动化应用的常见要求。

在非破坏性EMC测试期间,测试板利用台式DMM对2.5 V外部信号源进行采样。电压或电流测量值与DMM的测量值进行比较,以判断是否符合性能判据。

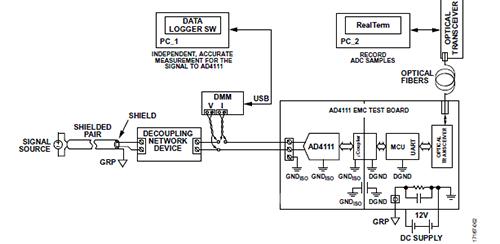

在辐射测试期间,电路板的模拟输入通道短接到隔离地。电路板与主机断开连接,而AD4111继续以1007 SPS的速率对每个通道中采样。此设置中的唯一辅助设备是12 V电池,用于为EMC测试板供电,假设其不会产生电磁辐射。EMC测试的通用设置如图3所示。

一对绞合引线(后接一个低通滤波器)探测精密信号源的输出。滤波后的输出通过一对绞合引线连接到DMM。DMM通过USB线缆连接到PC。主机上的RealTerm软件通过电隔离数据链路记录AD4111样本。对于每个EMC测试项目,EMC测试板都在电压输入模式和电流输入模式下进行测试。

图3.通用EMC测试设置

标准和性能指标

此测试板设计所针对的EMC和电磁干扰(EMI)测试项目、限值以及性能判据根据IEC 61131-2进行定义。根据该标准选择了以下六项适用的测试:

• IEC 61000-4-2

• IEC 61000-4-3

• IEC 61000-4-4

• IEC 61000-4-5

• IEC 61000-4-6

• CISPR 11

印刷电路板

AD4111 EMC测试板是与判据AD4111评估板EVAL-AD4111SDZ不同的独立设计,后者旨在提供最佳ADC性能,但未针对EMC和EMI测试进行优化。

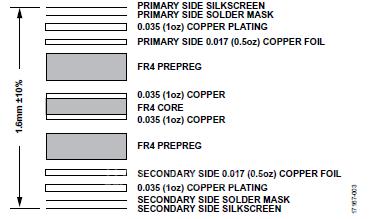

AD4111 EMC测试板基于FR4四层PCB。PCB堆叠如图4所示。顶面和底面均有0.5盎司铜箔。测试板的系统侧(由LDO、微处理器、ADuM5411的初级端和UART到USB收发器组成)位于四层结构上。内层有1盎司铜。这些层设计用于在不直接承载AD4111的电路板部分提供最佳EMC和EMI性能。

图堆叠

EMC板的现场侧包括AD4111及其全部外设,位于一个伪二层结构上,其中用于接地和电源平面的内层被完全蚀刻掉。这些层旨在演示AD4111在低成本双层PCB上实现额定工作性能以及EMC和EMI性能的可行性。

器件放置和布局注意事项

由于AD4111的分辨率较高且噪声电平很低,因此应谨慎对待去耦、接地和布局。模拟和数字部分在EMC板上是分开的,并局限在电路板的某些区域内。当使用2层以上的印刷电路板时,AD4111放置在一个实心接地层上, AVSS和DGND引脚均焊接到该接地层。AD4111的数字接口侧靠近隔离器,模拟侧面对电压和电流输入端子。电源通过0.1 μF电容与10 nF电容的并联组合去耦。两者都是低等效串联电阻(ESR)陶瓷电容,采用表面贴装封装,尽可能靠近AD4111电源引脚。

数字线路上的几十到几百欧姆的阻尼电阻会衰减互补金属氧化物半导体(CMOS)开关切换导致的电瞬态,帮助降低EMI。电阻还能减轻串行外设接口(SPI)中串联的铁氧体磁珠所引起的振铃效应。

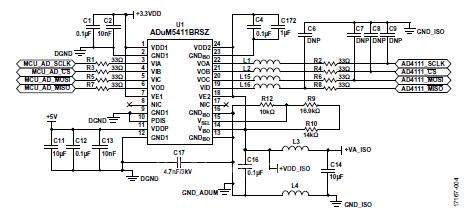

在参考ADuM5411数据手册中关于改善辐射发射性能的建议时需要特别注意。VDD1引脚和GND1引脚之间,VDDP引脚和GND1引脚之间,VISO引脚和GNDISO引脚之间,以及VDD2引脚和GNDISO之间引脚,有至少两个电容的并联组合用于抑制噪声和降低纹波。0.1μF和10 nF低ESR陶瓷电容在高频下提供低电感。10μF电容用于抑制纹波以及适当调节VDDP和VISO。这两个电容均尽可能靠近ADuM5411电源引脚放置,使PCB走线长度最短。

表面贴装铁氧体磁珠(BLM15HD182SN1D)与VISO和GNDISO引脚串联,以增加对高频电流的阻抗。在100 MHz到1 GHz之间,铁氧体磁珠的典型阻抗为2 kΩ,可降低125 MHz初级侧开关频率以及250 MHz次级侧整流频率和谐波的辐射。VISO通过短走线直接为VDD2供电。GNDISO(引脚23)内部连接到其他GNDISO引脚。引脚23仅连接到旁路电容,如图5所示。

高压表面贴片(SMT)电容直接连接在GND1(引脚12)和GNDISO(引脚13)之间,以获得最佳性能。为了进一步降低辐射,可以运用PCB拼接电容,详见应用笔记AN-0971。

图5411旁路和外设

其他器件注意事项

AD4111 EMC测试板采用0.1μF、50 V/X5R、10%、低ESR陶瓷电容,封装尺寸C0402,作为测试板现场侧的去耦电容。使用低ESR电容是权衡性能、降额、成本和节省空间等因素的结果。系统微处理器侧的去耦电容为0.1μF、50 V/X7R、10%、低ESR陶瓷电容,封装尺寸为C0603。

电压源保护

EMC和EMI评估与演示的范围集中在AD4111及其配套器件上。AD4111 EMC测试板上的电源电路为电路板功能提供必要的电压。这些电源电路的稳健性无意与工业自动化控制系统中的电源模块或背板电源相媲美,故仅为供电电路实现了基本保护。1 nF电容放置在电源输入端子的每个引脚旁,连接到受保护地,瞬态能量可通过3.3 nF/3 kV电容放电至地。4.7 MΩ电阻将能量释放到大地,以免其在受保护地上积聚。正向串联二极管以防止电源输入接线错误。SMBJ26CA瞬态电压抑制(TVS)二极管用于箝位瞬态电压,使之不高于24 V(标称值)。共模电感阻止下游电路的辐射逸出。电感之后的第二个SMCJ26CA TVS二极管为瞬态提供进一步的箝位。

ESD保护

EMC测试板上必须存在适当的ESD保护电路。保护由限流电阻、瞬态电压箝位和瞬态能量转移电容组成。

针对AD4111电压输入通道中的EMC和EMI,最少须有三个元件:一个180Ω电阻、一个4.7 nF电容和一个TVS器件。AD4111 VINx引脚和端子板之间的走线上的180Ω电阻与4.7 nF/50 V C0G GRT155R71H472KE01D电容一起为ADC提供抗混叠滤波。在EMC测试期间,RC滤波器可以衰减RF干扰。由于AD4111 VINx引脚内部连接到约1 MΩ电阻,所以180Ω串联电阻在AD4111和TVS箝位的高电压之间会提供一些额外的隔离。在EMC事件期间,TVS器件对于箝位电路板上的电瞬态至关重要。在AD4111和输入端子板之间插入SMAJ33CA-TR。用短而粗的走线将TVS引脚连到VINx终端引脚。

针对AD4111电流输入通道中的EMC和EMI,最少须有四个元件:一个PTC可复位保险丝、一个180Ω电阻、一个TVS器件和一个GRM1555C1H471JA01D电容。当流过其中的电流超过150 mA时,保险丝断路。AD4111 IINx引脚与端子板之间的走线上的180 Ω电阻有助于限制进出器件的瞬态电流,因为IINx的输入电阻约为60 Ω。在EMC事件期间,TVS器件对于箝位电路板上的电瞬态至关重要。在输入端子板之后和限流电阻之前插入SMA6J10A-TR。用短而粗的走线将TVS引脚连到VINx终端。位于限流电阻之后的470 pF/50 V C0G GRM1555C1H471JA01D电容将少量高频瞬态转移到隔离接地。

(转载)