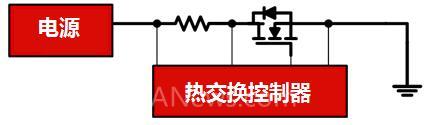

当电源与其负载突然断开时,电路寄生电感元件上的大电流摆动会产生巨大的尖峰电压,对电路上的电子元件造成十分不利的影响。与电池保护应用类似,此处MOSFET可以将输入电源与其他电路隔离开来。但此时,FET的作用并不是立即断开输入与输出之间的连接,而是减轻那些具有破坏力的浪涌电流带来的严重后果。这需要通过一个控制器来调节输入电压(VIN)和输出电压(VOUT)之间MOSFET上的栅源偏压,使MOSFET处于饱和状态,从而阻止可能通过的电流(见图1)。

图1:简化的热插拔电路

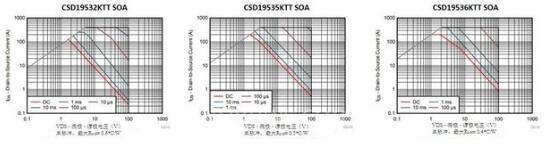

首先要为FET考虑的是选择合适的击穿电压,一般为最大输入电压的1.5到2倍。例如,12V系统通常为25V或30V FET,而48V系统通常为100V或在某些情况下达到150V FET。下一个考虑因素应该是MOSFET的安全工作区(SOA),如数据表中的一条曲线。它特别有助于指示MOSFET在短时功率浪涌期间是如何影响热击穿的,这与在热插拔应用中必须吸收的情况并无二致。由于安全操作区域(SOA)是进行适当选择最重要的标准,请参照了解MOSFET数据表-SOA图,该文详细介绍TI如何进行测量,然后生成设备数据表中显示的MOSFET的SOA。

对于设计师而言,关键的问题是FET可能会经受的最大浪涌电流(或预计会限制到输出)是多大,以及这种浪涌会持续多久。了解了这些信息,就可以相对简单地在设备数据表的SOA图上查找相应的电流和电压差。

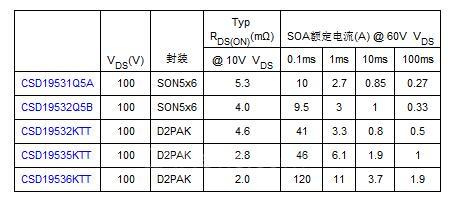

例如,如果设计输入电压为48V,并且希望在8ms内限制输出电流不超过2A,设计师可以参考CSD19532KTT、CSD19535KTT和CSD19536KTT SOA的10ms曲线(图2),并推断出后两种设备可能行得通,而CSD19532KTT则不行。由于CSD19535KTT已经拥有足够余量,对此种应用来说,更昂贵的CSD19536KTT可能提供过高的性能。

图2:三种不同100V D2PAK MOSFET的SOA

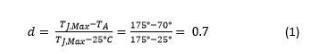

假定环境温度为25˚C,与在数据表上测量SOA的情况相同。由于最终应用可能暴露于更热的环境中,所以必须按照环境温度与FET最大结温之比,按比例为SOA降额。例如,最终系统的最高环境温度是70˚C,可以使用公式1为SOA曲线降额:

SOA曲线降额

在这种情况下,CSD19535KTT的10ms,48V能力将从~2.5A降至~1.8A。由此推断出特定的FET可能不再适合该应用,从而设计师应该改选CSD19536KTT。

值得注意的是,这种降额方法假设MOSFET恰好在最大结温下发生故障,虽然通常不会如此。假设在SOA测试中测得的失效点实际上发生在200˚C或其他任意较高温度下,计算的降额将更接近统一。也就是说,这种降额方法的计算不是保守的算法。

SOA还将决定MOSFET封装类型。D2PAK封装可以容纳大型硅芯片,所以它们在更高功率的应用中非常流行。较小的5mm×6mm和3.3mm×3.3mm四方扁平无引线(QFN)封装更适合低功率应用。为抵御小于5 - 10A的浪涌电流,FET通常与控制器集成在一起。

以下是几个注意点:

当针对热插拔应用时,对于FET在饱和区工作的任何情况,设计师都可以使用相同的SOA选择过程,甚至可以为OR-ing应用、以太网供电(PoE)以及低速开关应用(如电机控制)使用相同的FET选择方法,在MOSFET关断期间,会出现相当高的VDS和IDS的重叠。

热插拔是一种倾向于使用表面贴装FET的应用,而不是通孔FET(如TO-220或I-PAK封装)。原因在于短脉冲持续时间和热击穿事件发生的加热非常有限。换句话说,从硅结到外壳的电容热阻元件可以防止热量快速散失到电路板或散热片中以冷却结点。芯片尺寸的函数 - 结到外壳的热阻抗(RθJC)很重要,但封装、电路板和系统散热环境的函数 - 结到环境热阻抗(RθJA)要小得多。出于同样的原因,很难看到散热片用于这些应用。

设计人员经常假定目录中最低电阻的MOSFET将具有最强的SOA。这背后的逻辑是 - 在相同的硅片生产中较低的电阻通常表明封装内部有较大的硅芯片,这确实产生了更好的SOA性能和更低的结至外壳热阻抗。然而,随着硅片的更新迭代提高了单位面积电阻(RSP),硅片也倾向于增加电池密度。硅芯片内部的单元结构越密集,芯片越容易发生热击穿。这就是为什么具有更高电阻的旧一代FET有时也具有更好SOA性能的原因。总之,调查和比较SOA是非常有必要的。

请在TI官网了解更多各种热插拔控制器的信息。本文末尾的表1-3重点介绍了用于热插拔的一些设备,它们为SOA功能提供了部分参考值。

更多信息请查阅MOSFET选项博客系列。

表1:用于12V热插拔的MOSFET

表2:用于24V热插拔的MOSFET

表3:用于48V热插拔的MOSFET

(转载)