尽管全球经济的持续疲软拖累了半导体市场景气指数,但有一个领域却风景独好,那就是物联网。业界知名的半导体市场调研机构IC Insights对物联网市场给予极为乐观的预期,该公司的预测认为物联网半导体销售在2016年将增长19.9%,市场整体规模到2019年将达到296亿美元。

然而,物联网市场增长并非如预期一帆风顺,正如IC Insights已将其市场预期从之前的增长21.1%下调到19.9%。除了经济大环境影响,物联网相关应用技术本身在成熟度、功耗、成本、尺寸、封装等方面,依然面临不同程度的挑战,半导体原厂和方案商解决这些挑战上的技术能力,同样对市场竞争产生了非常重要的影响。三重富士通半导体公司(MIFS)市场总监谢杰在近日的一场演讲上,特别就这些问题进行了阐述:“包括MIFS在内,业界领先的代工厂商都在尝试突破工艺上的局限性,帮助半导体方案厂商赢得物联网这个巨量市场机遇。”

谢杰:“MIFS为碎片化物联网SOC定制了独特工艺。”

物联网芯片“碎片化”之困

谢杰的演讲主题为“为碎片化物联网SOC应运而生的MIFS特色工艺”,“碎片化”这个提法吸引了众多与会人士的关注。“物联网应用场景广泛而丰富,不同应用领域的客户对芯片方案的细节有不同要求,导致很多芯片专为满足小众市场设计,生产量不能扩大,因而芯片的批量生产被严重碎片化。” 谢杰解释道。事实上,这也是业界的共识,虽然物联网拥有巨大的市场潜力,但物联网与过去的手机、PC等产品领域存在一个巨大的差别,那就是该领域的应用非常分散。“这导致的结果是,芯片制造的NRE成本很高,而且很多代工厂不愿意接这种难以上量的订单。” 谢杰进一步指出。

关于碎片化带来的挑战,业界有过很多思考。早前就有业界人士指出,物联网之所以发展得不如想象中那么好,其中一个重要原因就是“碎片化”的阻碍。然而,“碎片化”却是物联网的“天性”——传感器多种多样,无线连接标准林立,应用类别千差万别——这给芯片方案设计和终端产品设计均带来挑战。“我们看好物联网的未来,希望利用成本优势兼制程优势,帮助中国客户解决物联网应用碎片化对流片所带来的挑战。”谢杰表示,他将MIFS的代工服务优势总结为 “媲美中国本土制造的成本,兼具日本制造的品质”。

重要事情说三遍:低功耗、低功耗、低功耗

绿色环保设计理念已深入人心,低功耗挑战似乎并不是物联网应用的“专利”。然而,事实上物联网的独特性注定了其大量应用对功耗特别敏感,甚至为扩大物联网应用,行业内为低功耗“操碎了心”——WiFi联盟正式发布了主打低功耗特性的802.11ah WiFi标准;蓝牙标准组织特别针对心率监控器或计步器等使用钮扣式电池的应用定制了Bluetooth Smart标准;NB-IoT低功耗广域网技术的推出让竞争技术备受压力;……而在传感器和MCU等物联网方案的关键器件领域,相关的低功耗产品和技术的竞争更是日趋激烈。

物联网的大热,中国IC设计公司也涌现出越来越多的玩家进入传感器、低功耗MCU、无线连接等芯片方案领域,以追逐移动互联时代智能化和物联网大潮带来的商机。然而,苛刻的低功耗特性要求可能成为一道无形的门槛。“这里面既涉及到电路的低功耗优化设计knowhow,更重要的还有芯片制造中如何实现低功耗的制程优势。”谢杰指出。他还用MIFS某欧洲著名企业客户的案例来说明物联网典型应用中的低功耗敏感性——针对心脏起搏器中的一款监测芯片,为了显著延长电池替换周期,其生产制程需要帮助实现超低待机功耗和工作功耗。“哪怕多延长几天的电池寿命,对病人来说都具有很大的意义。最终,我们DDC(全耗尽沟道)的卓越低功耗优势被他们选中。”谢杰分享道。

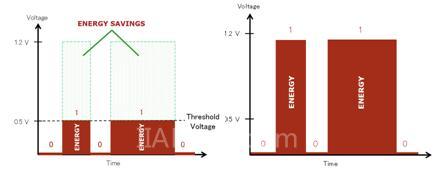

为应对这些专门应用所带来的挑战,很多代工厂加入低功耗制造新制程的研发上,MIFS也不例外,据悉该公司是全球唯一以DDC技术达到超低电压和超低漏电晶体管技术的代工厂。谢杰对其低功耗工艺的深度专业分析占据了其演讲的主要部分,也是吸引现场芯片设计厂商关注的焦点。谢杰给出了最直观的数据——与传统1.2V工作电压的芯片相比,基于DDC低功耗工艺的芯片可以在0.5V工作,功耗得以大大降低。“DDC超低漏电流保证了芯片在休眠和工作状态下很小的功耗,其超低的工作电压对降低功耗非常关键。”谢杰解释道。据其透露,在相同的信号眼图测试中,基于DDC技术的45nm的芯片甚至在0.4V的电源电压下仍可以观察到信号眼图,而某大厂的芯片在0.6V的电源电压下已停止工作。

基于DDC技术的Sub-threshold电路可以显著降低芯片功耗。

据悉,MIFS的超级低功耗DDC工艺新技术是由美国SuVolta开发,MIFS已经买断该专利。DDC CMOS晶体管构成的超低功耗CMOS技术,能控制晶体管的阈值(Vt)偏差并提高载体的移动度。“如果采用此项技术,运行时的功耗最多可比一般的集成电路降低50%却不会降低IC的运行速度。”谢杰表示。MIFS进一步改善了DDC技术,全新开发了漏电电流可减少2位数的DDC晶体管,而这种DDC晶体管最适合Sub-threshold电路。 “MIFS独家拥有专利的新制程使得‘Half the POWER, All the Performance’变成现实。”谢杰说道。

如何满足物联网市场的低成本、快市场要求?

业界有观点认为,49%的物联网产品在2020年以前的年出货量会低于1亿片,物联网的严重碎片化特点导致极高的成本敏感性,包括应用市场的成本敏感,以及芯片流片的成本敏感。如果采用最先进的芯片生产工艺,无疑制造成本会极高,在不确定的市场,甚至是不确定的玩家环境下,芯片公司要尽可能地降低流片成本和风险。为更好地服务于中国本土中小企业的芯片“碎片化”的制造需求,MIFS特别在2016年推出旨在降低流片成本的“Shuttle Service”务——用降低芯片成本来验证客户设计的手段,采用多项设计共享晶圆、掩模以控制成本的流片服务项目,包括最新的55nm DDC和40nm CMOS工艺技术。

让芯片实现快速流片以应对物联网快速变化的市场需求,代工厂的服务能力(包括基础IP库资源)很关键。在Gartner今年发布的全球前十大半导体代工厂名单中,三重富士通的排名从去年的第十名前进到第八名。“富士通的优质代工资源获得业界的认可,这些资源帮助我们与日本及欧洲很多知名厂商开展了大量的合作。”谢杰分享道,“特别是符合物联网应用的一些独特优势资源,首次针对IC设计企业全面开放,另外我们全力打造的生态系统资源,也正在获得越来越多厂商的关注。”

MIFS以独特的定位和制程优势,跃升为全球代工企业第八位。

除了谢杰在演讲中重点分享的DDC技术以及嵌入式存储技术,他在与国内某厂商交流中还分享了一个能体现三重富士通在图像传感器和图像处理器芯片领域显著优势的案例。“全球知名的Milbeaut系列ISP技术芯片一直是我们在做代工,当前全球很多的CMOS 图像传感器(CIS)和图像处理器(ISP)都是我们代工的。”谢杰介绍,“随着图像传感器和图像处理技术在车联网(汽车ADAS)、无人机等领域中被更广泛地应用,中国企业在这个领域将有很大的发展空间,而三重富士通拥有的图像处理芯片相关的制造工艺和IP资源这些不可替代的优势,完全可以助力中国企业腾飞。”

Milbeaut图像处理器代工的丰富经验和IP资源让MIFS占据全球ISP主要代工市场。

类似的IP资源也是集成电路企业寻求制造代工时的一个重要参考,代工企业也各自凸显在这方面的资源。谢杰演讲中特别强调了MIFS在该领域近年来突出的发展成就,除了DDC外,MIFS低成本嵌入式存储、低成本无线连接以及针对AEC-Q100 Grade1或2的汽车半导体代工制程技术也是最受物联网业界看好的制程技术优势。“MIFS覆盖了从40-90nm节点的低功耗CMOS技术,提供独具特色的eNVM、RF工艺选项,如碳纳米管存储技术、毫米波射频技术。这些对很多物联网集成电路来说都非常关键。” 谢杰指出,“MIFS本身拥有丰富的基础IP库,我们还加强了与Synopsys、Kilopass、Faraday等在基础IP上的合作,全面解决了物联网芯片制造上的IP资源需求。”

本文小结

最新数据表明,中国集成电路设计企业全行业销售1518.52亿元,增长达23.04%。然而另一方面,中国集成电路设计企业数量从2015年的736家大幅增加到1362家,其中,中小规模的设计企业占据绝大多数。“以物联网应用为代表的产业热潮正在给中国集成电路企业带来大好机遇,但从我们与本土客户的交流来看,机遇与挑战确实并存,特别是小规模市场体量和碎片化市场需求所导致的流片成本压力。”谢杰指出,“我们抛开了传统IDM公司的业务模式,愿为中国本土IC设计公司的成长提供专业代工服务,并以灵活的商业模式,致力于成为本土半导体公司强有力的合作伙伴。”

(转载)